PRODUCT BRIEF

LICENSABLE

INTELLECTUAL

PROPERTY

FOR FPGA, ASIC OR

ASSP DESIGNS

10G

Ultra-Low Latency

10G Ethernet MAC

and PCS

### **APPLICATIONS**

- **■** High Frequency Trading

- **Smart NIC**

- **■** Low-Latency Switches

# ULTRA-LOW LATENCY, HIGH-SPEED, FLEXIBILITY AND SCALABILITY.

The Ultra-Low Latency 10G Ethernet MAC and PCS is the industry leading solution for latency critical Ethernet applications. The core is designed using advanced design techniques leading to unmatched ultra-low gate count utilization and amazing latency performances.

The IP core can support full wire line speed with a 64-byte packet length. It also supports back-to-back or mixed length traffic with no dropped packets.

### **GENERAL FEATURES**

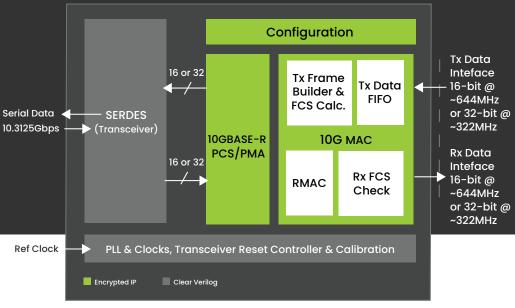

## User logic Interface

- AXI-4 Stream 16b @ ~644MHz

- AXI-4 Stream 32b @ ~322MHz

#### **SERDES Interface**

- 16b @ ~644MHz

- 32b @ ~322MHz

### Early SoP Indication (Tx)

Early SoF Detection (Rx)

10G Ethernet MAC and PCS

**Contact us for** a personalized evaluation and to discuss the best way to try our products.

# Configuration

**HIGH-LEVEL BLOCK DIAGRAM**

### **DELIVERABLES**

- Datasheet & user guide

- Encrypted Verilog

- Constraints file

- Reference design

- Technical support

- Optional IP design customization

### **MAC FEATURES**

- Deficit idle counter (DIC) to maintain a 12-byte inter-packet gap (IPG) average

- User facing logic interface 16-bit @ 644.531250MHz or 32-bit @ 322.265625MHz

- Tx Frame Check Sequence (FCS) computation and insertion

- Rx FCS error detection

- Fully compatible with Orthogone 10G TCP/UDP IP core

### **PCS FEATURES**

- Supports 10GBASE-R PHY based on 64B/66B encoding and scrambling

- Supports block synchronization

sales@orthogone.com 514.316.1917 x777

### PERFORMANCES OVERVIEW EXAMPLE

| Device<br>Family | Rate<br>[Gbps] | SERDES<br>Width | AXI-4<br>Stream<br>Width | Resources Utilization |      |      | Core clock | Wire to Wire          |

|------------------|----------------|-----------------|--------------------------|-----------------------|------|------|------------|-----------------------|

|                  |                |                 |                          | LUTs                  | FFs  | BRAM | [MHz]      | Round-Trip<br>Latency |

| UltraScale +     | 10-Gbps        | 16b             | 16b                      | 1.4k                  | 1.1k | 0    | 644.531    | 20.2ns <sup>(1)</sup> |

| UltraScale +     | 10-Gbps        | 16b             | 32b                      | 1.5k                  | 1.1k | 0    | 644.531    | 34.1ns <sup>(2)</sup> |

- (1) Latency: GTY + MAC/PCS (Measured from TxSoP to RxSoF using serial loopback)

- (2) Latency: GTY + MAC/PCS + CDC (Measured from TxSoP to RxSoP using serial loopback)